| Upstream PCIe interface |

- 4-lane PCI Express

- PCIe Gen 1 (2.5GT/s)

- PCIe Gen 2 (5.0GT/s)

|

| Downstream Port interface |

- Two USB 3.0 Cable Ports (A-type Receptacle, USB IF TID 360000145)

- IOI Proprietary Dual-lane Internal PCIe Ports

- 10X2_19pin Header (Pitch=2.0mm)

- Two PCIe x1

- Dual-lane Internal PCIe Port

- PCIe Gen 1 (2.5GT/s)

- PCIe Gen 2 (5.0GT/s)

|

USB Features

(Renesas uPD720202; USB IF TID 380000043) |

- Compliant with USB 3.0 Specification Revision 1.0

- Compliant with Intel’s eXtensible Host Controller Interface (xHCI) specification Revision 1.0

- Each USB port supporting SS/HS/FS/LS data rates (5Gbps/480Mbps/12Mbps/1.5Mbps)

- USB Data Transfer Rate

- Low-speed (1.5 Mbps)

- Full-speed (12.0 Mbps)

- High-speed (480.0 Mbps)

- Super-speed (5.0 Gbps)

|

USB Bus Power Input (5V) |

SATA 15pin Power Connector

|

| PCIe Features |

- Standards compliant

- Compliant with PCI Express Base Specification Revision 2.1

- Compliant with PCI Express CEM Specification Revision 2.0

- Compliant with PCI-toPCI Bridge Architecture Specification Revision 1.2

- Compliant with Advanced Configuration Power Interface (ACPI) Specification

- PCI Power Management Spec r1.2

- PCI Express Power Management

- Link power management states: L0, L0s, L1, L2/L3 Ready, and L3

- Device states: D0 and D3hot

- Active state power management for L0s and L1 states

- Port Arbitration Round Robin (RR) and Weighted RR and Time-based Weighted RR

- Extended Virtual Channel capability

- Two Virtual Channels (VC) and Eight Traffic Class (TC) support

- Disabled VCs’ buffer is assigned to enabled VCs for resource sharing

- Independent TC/VC mapping for each port

- Provides VC arbitration selection: Strict Priority, Round Robin (RR) and Programmable Weighted Round-Robin

- Supports Isochronous Traffic

- Isochronous traffic class mapped to VC1 only

- Strict time based credit policing

- Supports “Cut-through”(Default) as well as “Store and Forward” mode for switching packets

- Peer-to-peer switching between any two downstream ports

- Supports up to 512-byte maximum payload size (setting to 256-byte)

- Enhanced Features

- 150ns typical latency for packet running through switch without blocking

- Supports Access Control Service (ACS) for peer-to-peer traffic

- Supports Address Translation (AT) packet for SR-IOV application

- Supports OBFF and LTR

|

Port (Lane) Status LEDs |

Port (Lane) LEDs

- PORT0 LED : Lane0~3

- PORT1 LED : Lane4

- PORT2 LED : Lane5

- PORT3 LED : Lane6

- PORT4 LED : Lane7

LED Status

- Blink: Gen 1 speed

- Solid: Gen 2 speed

|

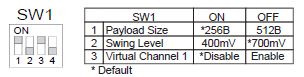

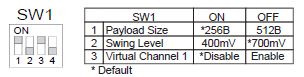

| Switch |

- Payload Size

Supports up to 512-byte maximum payload size (Default is 256-byte)

- Swing Level

700mV: In full swing signaling mode, the transmitters implement de-emphasis.

400mV: In half swing signaling mode, the transmitters not implement de-emphasis.

- Virtual Channel 1

Disable: The unused VC1 queues (buffer) can be reassigned to VC0 and enable each of

the ingress ports to handle more data traffic bursts. This virtual channel resource

relocation feature enhances the performance of the PCIe Switch further.

Enable: Isochronous traffic class mapped to VC1 only

|

| Computer Platform Requirements |

Desktop computer equipped with a PCIe 2.0/3.0 x4, x8, x16 slot |