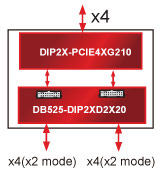

DIP2X-PCIE4XG210

| Upstream PCIe interface |

- 4-lane PCI Express

- PCIe Gen 1 (2.5GT/s)

- PCIe Gen 2 (5.0GT/s)

|

| Downstream PCIe interface |

- Two IOI Proprietary Dual-lane Internal PCIe Ports

(PCIe-1~2)

- 10X2_19pin Header (Pitch=2.0mm)

- 2-lane PCIe (PCIe x2)

- Each Dual-lane Internal PCIe Port

- PCIe Gen 1 (2.5GT/s)

- PCIe Gen 2 (5.0GT/s)

|

| Key Features |

- Industry Specifications Compliance

- PCI Express® Base Specification, Revision 2.1

- PCI Express CEM Specification, Revision 2.0

- PCI-to-PCI Bridge Architecture Spec., Rev 1.2

- Advanced Configuration Power Interface (ACPI) Specification

- EEPROM interface support

- PCISIG PCI Express 2.1 certificated

- Integrated 100MHz Clock buffer for each downstream port

- Reliability, Availability and Serviceability

- Supports Data Poisoning and End-to-End CRC

- Advanced Error Reporting and Logging

- Device State Power Management

- Supports D0, D3Hot and D3Cold device power states

- Advanced Power Savings

- Empty downstream ports are set to idle

- Programmable driver current and de-emphasis level at each individual port

- Port Arbitration: Round Robin (RR), Weighted RR and

Time-based Weighted RR

- Extended Virtual Channel capability

- Two Virtual Channels (VC) and Eight Traffic Class (TC) support

- Independent TC/VC mapping for each port

- Supports Isochronous Traffic

- Isochronous traffic class mapped to VC1 only

- Supports “Cut-through”(Default) as well as “Store and Forward” mode for switching packets

- Peer-to-peer switching between any two downstream ports

- Supports up to 512-byte maximum payload size

- Power Dissipation: 1.1 W typical in L0 normal mode

(Including clock buffer Pd)

- 150ns typical latency for packet running through switch without blocking

- Link Power Management

- Supports L0, L0s, L1, L2, L2/L3Ready and L3 link power states

- Active state power management for L0s and L1 states

- Supports PCI-PM

- Supports Device Specific PME Turn-Off Message for each downstream port

- Support Access Control Service (ACS) for peer-to-peer traffic

- Support Address Translation (AT) packet for SR-IOV application

- Support OBFF and LTR

|

| Computer Platform Requirements |

Desktop computer equipped with a PCIe 2.0/3.0 x4, x8, x16 slot |

DB525-DIPD2XD2X20

| Upstream host connector |

- Two dual-lane Internal PCIe ports ( IOI Proprietary)

- 10X2_19pin Header (Pitch=2.0mm)

- 2-lane PCIe (PCIe x2)

|

Downstream Internal PCIe bus interface |

- Two PCIe x4 slots (x2 mode)

- Supports 2-lane PCI Express bandwidth

|

Power connector |

- One SATA 15pin power connector

Note: it requires power (+12V, +5V, +3.3V)

|

| Form factor |

- One 5.25" ODD form factor

- 146.6(W) x 42(H) x 175 (D) mm

- NW: 352g

|

|