| Upstream PCIe interface |

- 4-lane PCI Express

- Throughput

- PCIe Gen 1 (2.5GT/s)

- PCIe Gen 2 (5.0GT/s)

|

| Downstream PCIe interface |

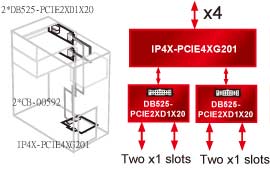

- Two IOI Proprietary Dual-lane Internal PCIe Ports

(PCIe-1~2)

- 10X2_19pin Header (Pitch=2.0mm)

- 2-lane PCIe (Two PCIe x1)

- Each Dual-lane Internal PCIe Ports

- PCIe Gen 1 (2.5GT/s)

- PCIe Gen 2 (5.0GT/s)

|

| Key Features |

- Standards Compliant

- PCI Express Base Specification r2.0 (Backwards compatible with PCIe r1.0a/1.1)

- PCI Power Management Spec r1.2

- Microsoft Vista Compliant

- Supports Access Control Services

- Dynamic link-width control

- Dynamic SerDes Speed Control

- High Performance

- Non-blocking internal architecture

- Full line rate on all ports

- Cut-Thru latency: 140ns for Link widths of x4 to x1

- Maximum Payload Size - 2,048 bytes

- Read Pacing (intelligent bandwidth allocation)

- Dual Cast

- Dynamic Buffer Pool Architecture for faster credit updates

- PCI Express Power Management

- Link power management states: L0, L0s, L1, L2/L3 Ready, and L3 (with Vaux not supported)

- Device power management states: D0 and D3hot

- Active State Power Management (ASPM)

- Quality of Service (QoS)

- Two Virtual Channels (VC) per port

- Eight Traffic Classes per port

- Weighted Round-Robin Port & VC Arbitration

|

Lane Status LEDs (for PCB v1.1)

- Blink: Gen 1 speed

- Solid: Gen 2 speed

|

- Upstream Lane Status LEDs

- LED-Lane0: Upstream x1 Status LED

- LED-Lane3: Upstream x4 Status LED

|

| Computer Platform Requirements |

Desktop computer equipped with a PCIe 2.0/3.0 x4, x8, x16 slot |

| Dimensions |

- 64.5(H)x81(L) mm

- NW: 48.5g

|